ダイオード 耐圧計算

ダイオードの耐圧計算

以下コピペ用~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

■ダイオードの耐圧

・ダイオードの耐圧は、教科書では図1みたいな簡易構造で計算する。

・でも実際の耐圧は、以下の様な理由で、計算値よりも耐圧が低くなることが多い。

①フィールドプレートの端に電界が集中する

②その直下付近のシリコンに大きな電界が生じる

③その付近の空乏層に、電荷のパスが生じ易くなる(ionization integral)

⇒これら①~③がデバイスのウィークポイントになる。

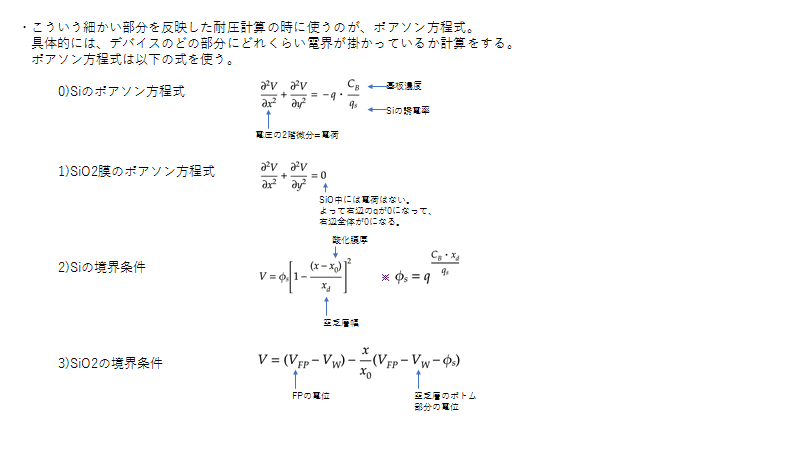

・こういう細かい部分を反映した耐圧計算の時に使うのが、ポアソン方程式。

具体的には、デバイスのどの部分にどれくらい電界が掛かっているか計算をする。

・このポアソン方程式から計算した、ダイオード耐圧-各種パラメータ の相関が

以下の通り。

■シリコンの挙動

①・「基板濃度を上げると、耐圧が下がる」傾向。

・この傾向は、

基板濃度↑⇒空乏層が伸びなくなる⇒耐圧↓

というシリコン(PN接合)の物性に起因する。

■酸化膜の影響

②・「酸化膜厚が厚くなると、耐圧が上昇する」という傾向。

・これは、酸化膜があることで酸化膜で電圧降下が起こり、

PN接合部(空乏層)の電界が緩和されるという効果に起因する。

※特にデバイスのウィークポイントであるFP直下の部分の電界集中

が緩和されるのが好影響。なので酸化膜厚が増加するとデバイスの

耐圧が上昇する。

※式は左下の通り。

③・「(酸化膜厚の厚いデバイスでは)基板濃度が1e16を超えると、

耐圧が上昇する」という傾向。

・これは基板濃度が1e16を超えると、左下式のEcritが上昇し、

酸化膜で大きく電圧降下する(=酸化膜が電圧を分担してくれる)

ようになり、PN接合部(空乏層)の電界が緩和されるという効果

があるから。

②③はいずれも酸化膜が原因でデバイス耐圧が変わっている。

こういう要素があるから、①のような単純なシリコンの物性だけでは

耐圧計算が出来ない。ポアソン方程式から算出された局所的な傾向を

考慮する必要がある。

SiC IGBT FET

- 作者: S.M.ジィー,S.M. Sze,南日康夫,川辺光央,長谷川文夫

- 出版社/メーカー: 産業図書

- 発売日: 2004/03/01

- メディア: 単行本

- 購入: 1人 クリック: 27回

- この商品を含むブログ (4件) を見る